London show news

Posted by Steve Revill Thu, 22 Oct 2015 20:04:00 GMT

We’re packing our kit ready for the London show, which starts at 11am on Saturday 24th October 2015 and look forward to seeing you there.

Read more...Posted by Steve Revill Thu, 22 Oct 2015 20:04:00 GMT

We’re packing our kit ready for the London show, which starts at 11am on Saturday 24th October 2015 and look forward to seeing you there.

Read more...Posted in Press release, Community | no comments

Posted by Steve Revill Sat, 01 Aug 2015 13:36:00 GMT

It’s always great to hear of RISC OS users from far flung places – it’s a useful reminder of the importance of internationalising applications for non native English speakers.

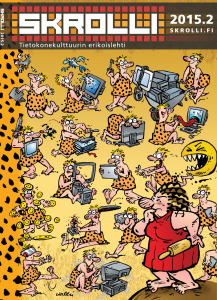

One recent example of this is the 5 page review of RISC OS Pico which features in the Skrolli computer magazine. RISC OS Pico was put together to coincide with the 50th anniversary of BASIC and recapture the halcyon days of MODE 7 home computing. The article Raspista vanhan ajan kotitietokone recounts home computers from the 1980’s and how well the feature of the built in BBC BASIC and its built in assembler compares with those original machines.

Ex pat user Kevin, who tipped off ROOL about this article, was pleased to add the Finnish for all sorts of RISC OS concepts to his vocabulary – they don’t tend to crop up in water cooler conversations.

For 9 euros you can buy a copy to read if you’re fluent in Finnish, but the example graphic program from the article (listing 1, listing 2) will run regardless.

The only complaint cited was that the MODE 7 character set didn’t cover the full Finnish alphabet. MODE 7 is emulated in software by the RISC OS kernel rather than using the SAA5050 chip as the BBC Micro did. Although German/Swedish/Italian/Belgian variants of the chip were produced, implementing a Finnish version in software is left as an exercise for the reader.

Posted by Steve Revill Sun, 05 Jul 2015 09:54:00 GMT

Starting from tomorrow, July 5th, the Iyonix, OMAP3, OMAP4 and Raspberry Pi development ROM images will be making use of “zero page relocation”, a change to the RISC OS memory map which moves the kernel’s “zero page” workspace away from address zero and up to the high end of the memory map. This greatly increases the system’s resilience to a common type of software bug known as a “null pointer dereference”. However, there is a catch: because the OS has always had memory mapped to address zero, large amounts of RISC OS software contains cases of “harmless” null pointer dereferences where the code reads from page zero and then does something insignificant with the result (usually ignoring it completely). With the new memory map, these programs will most likely cease to operate, exiting with a data abort as soon as they try to access page zero.

Since relocating zero page is very beneficial to the stability and security of the OS, the goal is to have the feature enabled for all future stable releases, starting with RISC OS 5.24. But due to the large amount of buggy software out there we can’t simply turn it on and be done with it – we need to have a transition period in which developers can fix their code without worrying about the fact their compilers, text editors, etc. are buggy too. We also need a way for regular users to get involved with the testing process.

With that in mind, we are putting into effect a two-phase testing process:

Phase 1 of the testing process begins tomorrow. Zero page relocation is enabled, but a compatibility/logging module (“ZeroPain”) is provided to you in order to allow most buggy software to continue to run unmodified. ZeroPain traps most attempts to read page zero and emulates the operation, providing a safe level of compatibility with the old memory map. And for any page zero access which it emulates, it adds an entry to a log file so that the user/developer is aware of the issue.

Phase 2 of the testing process is due to begin on 1st Jan, 2016. ZeroPain will refuse to run on any ROM built on or after that date. This will help to ensure that any previously unnoticed bugs are found and fixed prior to the release of RISC OS 5.24.

ZeroPain can be found within each ROM download archive. Make sure to install it before installing the new ROM, otherwise your system may not boot correctly. Please help ROOL make RISC OS a better OS by testing all your software and reporting any issues you find to the developers.

Modern ARM CPUs support a feature known as ‘high processor vectors’, whereby the processor vectors are moved from their old location at &0 to a new location at &FFFF0000. Zero page relocation within RISC OS makes use of this feature – without it we would still need some memory mapped to address zero in order to contain the processor vectors. Although high processor vectors is currently a requirement for zero page relocation, this is likely to change in the future, in order to support zero page relocation on the IOMD (RiscPC/A7000/RPCEmu) build of RISC OS.

OS_PlatformFeatures 0 can be used to determine whether high processor vectors are in use (flag returned in bit 20). Software which needs to interact with the processor vectors directly should use this to determine their location. The address of the processor vectors should not be used to infer the address of the zero page workspace, and vice-versa.

Apart from the change in location, the processor vectors continue to operate as normal – so for FIQ handlers, you can still rely on having 228 bytes of space available for your handler code (from &FFFF001C to &FFFF00FF inclusive). Also, for future compatibility, code should not assume that the processor vectors are readable from user mode – regardless of whether high processor vectors are in use or not.

Another change that is planned for RISC OS 5.24 is to re-enable support for unaligned loads/stores on ARMv6+. For the past few years this feature has been disabled by default, to protect you against potential compatibility issues with software which assumes the older ARMv5 “rotated load” behaviour is in effect. But we believe the time to re-enable the feature is drawing near – expect to see it happen sometime during the zero page relocation testing process. By re-enabling support for unaligned loads/stores the performance of some OS operations will be improved, and third-party software aimed at ARMv6+ can more easily make use of the feature.

Posted in Miscellaneous, New component, Community | 1 comment

Posted by Steve Revill Fri, 24 Apr 2015 20:47:00 GMT

RISC OS Open look forward to seeing you at the 20th Wakefield show, this Saturday 25th April 2015.

Read more...Posted in Press release, Community | no comments

Buy RISC OS Open merchandise here, including SD cards for Raspberry Pi and more.

Buy RISC OS Open merchandise here, including SD cards for Raspberry Pi and more.